在當今高效能運算和人工智慧蓬勃發展的背景下,CoWoS(Chip-on-Wafer-on-Substrate)作為一項先進的封裝技術,扮演著至關重要的角色。由台積電主導開發的這項技術,通過將多顆晶片整合於矽中介層上,不僅顯著提升了運算效能,還有效改善了散熱和功耗問題。隨著AI與5G需求的爆炸性增長,CoWoS技術的應用愈加廣泛,尤其是在高效能計算和資料中心領域。本文將深入探討CoWoS技術的核心概念、應用領域及其未來發展趨勢,揭示這項技術如何重塑半導體產業格局。

什麼是CoWoS?

CoWoS(Chip-on-Wafer-on-Substrate)是一種由臺積電主導開發的先進封裝技術,屬於2.5D封裝的範疇。它的主要特點是將多顆晶片堆疊在一個矽中介層上,再與基板相連接,以提升運算效能和散熱效果。這項技術能解決隨著半導體製程微縮所面臨的效能瓶頸,尤其在高速運算和人工智慧(AI)應用中,成為關鍵技術之一。

CoWoS技術的核心在於將多顆高效能晶片(如GPU或處理器)集成在一起,使得它們可以在同一個系統內進行更快速、更高效的數據交換。這不僅讓晶片的效能提高,也有助於解決功耗與熱管理的問題。因此,CoWoS技術廣泛應用於AI伺服器、資料中心和高效能計算領域。

隨著AI需求的爆炸性增長,NVIDIA等大廠對CoWoS技術的需求大幅增加,這也推動臺積電持續擴大其封裝產能,預計到2024年底,臺積電的CoWoS產能將達到24萬片以上,以滿足市場需求。

CoWoS Interposer是什麼?

CoWoS(Chip-on-Wafer-on-Substrate)是一種2.5D的先進封裝技術,用於將多個晶片(die)整合在一起。其核心概念是將多個晶片透過矽中介層(Interposer)堆疊在晶圓上,並在基板上進行封裝。這種技術的主要目的是改善晶片間的互聯密度和性能,特別適合高效能運算(HPC)、AI、5G等應用領域。

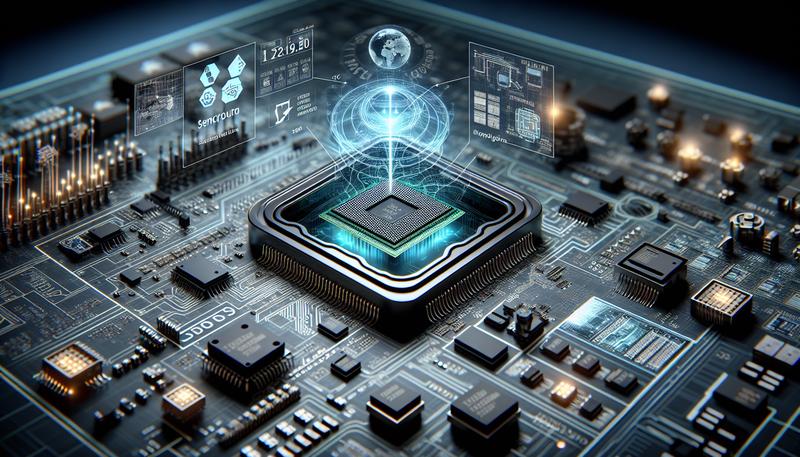

CoWoS的關鍵元件是「矽中介層」,它可以在多個晶片之間提供高速的訊號傳輸及電源管理,從而提高整體效能。這種技術透過晶片堆疊的方式,有效縮小了晶片體積並提升運算效率,是臺積電等領先半導體廠商的專利技術之一。

另外,CoWoS技術還結合了新型的熱介面材料(TIM)和多層金屬堆疊結構,以進一步解決高運算功率下的散熱和電阻問題,提升整體封裝的可靠性。目前,這種技術廣泛應用於NVIDIA H100等AI加速器中,成為半導體行業應對摩爾定律放緩的重要方案之一。

CoWoS先進封裝是什麼?

CoWoS(Chip-on-Wafer-on-Substrate)是一種先進的半導體封裝技術,旨在將多個晶片整合在一起,從而提升運算效能和節省空間。這種封裝技術的核心是透過矽中介層(Si Interposer)來將邏輯晶片和高頻寬記憶體(HBM)進行互連,並且使用矽通孔(TSV)技術來連接到基板,最終實現電路與外部的訊號連接。這樣的封裝方式讓晶片在保持高效能的同時,降低功耗與成本。

CoWoS是一種2.5D甚至3D的封裝技術,它通過將多個晶片橫向堆疊在中介層上(2.5D),或是垂直堆疊在一起(3D),來達到更高的晶片密度和更優的散熱效果。與傳統的單晶片設計相比,CoWoS不僅提升了晶片的效能,也解決了摩爾定律趨緩的問題,因此廣泛應用於高效能運算(HPC)、AI伺服器、資料中心等領域。

隨著AI運算需求的爆發,NVIDIA等公司開始在最新的GPU中大量採用CoWoS技術,如H100 GPU等。臺積電作為這項技術的主要推動者,不斷擴充其先進封裝產能,以滿足市場對這類高階封裝技術的需求。

臺積電CoWoS是什麼?

CoWoS(Chip-on-Wafer-on-Substrate)是臺積電的一種先進封裝技術,用於將多個不同功能的晶片(如CPU、GPU和高頻寬記憶體HBM)整合在一個基板上,實現2.5D或3D的晶片堆疊。這項技術可以顯著提高運算效能並降低功耗,非常適合高效能運算(HPC)和人工智慧(AI)應用。

CoWoS的封裝過程分為兩個階段:首先是將晶片堆疊在晶圓上,稱為「Chip-on-Wafer」(CoW),接著再將這些已堆疊的晶片封裝在基板上,稱為「Wafer-on-Substrate」(WoS)。這種技術利用矽穿孔(Through-Silicon Vias, TSV)和微凸塊(Micro-bumps)來實現晶片之間的垂直互聯。

臺積電的CoWoS技術在AI晶片領域的需求極高,特別是輝達(NVIDIA)和AMD的高階GPU,像H100、A100等產品都依賴這項技術。隨著AI運算需求的快速增長,臺積電的CoWoS產能面臨供不應求的壓力,因此臺積電積極擴充產能,計劃到2024年底將月產能擴增至3.5萬片,以滿足全球市場的需求。

這項技術不僅推動了臺積電在AI和高性能計算市場的領先地位,也使得臺積電在全球先進封裝技術領域獨佔鰲頭。

CoWoS幾奈米?

CoWoS(Chip-on-Wafer-on-Substrate)是一種先進封裝技術,能夠將不同製程節點的晶片集成在一起。它常應用於7奈米及以下的製程中,以實現高效能運算所需的多層晶片堆疊。例如,CoWoS技術可以整合5奈米的運算晶片與12奈米的射頻晶片,從而有效提升運算速度並降低功耗。

此外,臺積電的CoWoS技術目前支援的最先進製程已經達到5奈米,並且在AI晶片的需求驅動下,未來幾年將持續擴大這一技術的應用。

CoWoS一片多少錢?

臺積電的CoWoS(Chip-on-Wafer-on-Substrate)先進封裝技術,由於其高度複雜的製程和對AI晶片的強大需求,價格高昂。根據業內報導,臺積電的CoWoS封裝成本約是傳統封裝的兩倍。目前每片CoWoS的封裝價格介於 5,000美元到10,000美元 之間,具體價格會依照客戶需求和封裝的技術要求有所不同。

此外,隨著AI應用快速增長,臺積電的CoWoS產能需求持續上升,預計未來幾年價格還會隨之上調,漲幅可能達到10%至20%。這一價格升高的趨勢反映了AI加速器和高效能運算(HPC)需求的快速增長。

總結

CoWoS(Chip-on-Wafer-on-Substrate)是台積電主導開發的先進封裝技術,屬於2.5D封裝,旨在將多顆晶片整合在矽中介層上,並與基板連接,以提升運算效能和散熱效果。此技術特別適用於高效能運算(HPC)、人工智慧(AI)及5G應用,能有效克服隨著微縮製程而產生的效能瓶頸。CoWoS的矽中介層提供高效能晶片間的快速訊號傳輸,並解決功耗與熱管理問題,廣泛應用於NVIDIA等公司的高端GPU。隨著AI需求激增,台積電也在持續擴充CoWoS產能,預計到2024年底達到24萬片,以應對市場的需求。其封裝成本較傳統技術高,介於5000至10000美元,且未來價格料將因需求上升而增加。